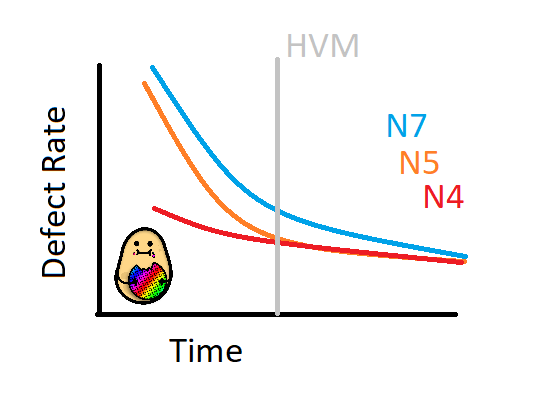

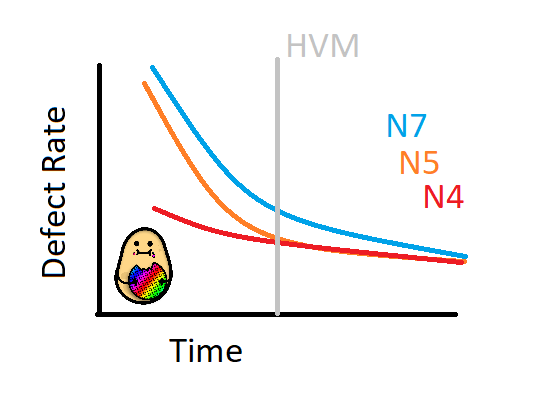

𝐷𝑟. 𝐼𝑎𝑛 𝐶𝑢𝑡𝑟𝑒𝑠𝑠 on X: Here's a mockup of what was shown regarding TSMC's N4 D0 defect rate compared to previous nodes. Grey line shows high volume manufacturing start (N4 beyond HVM

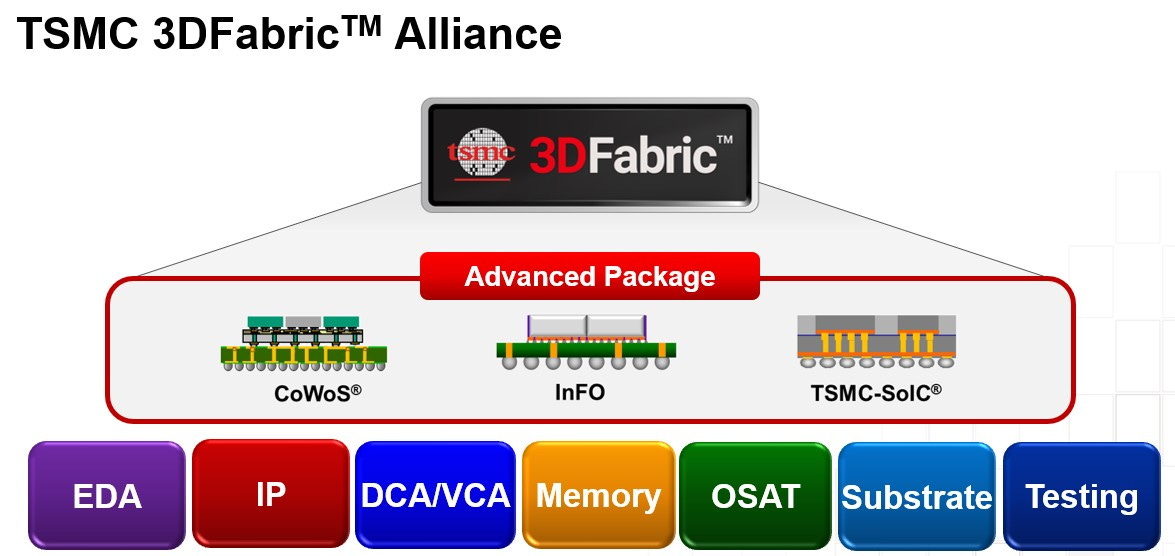

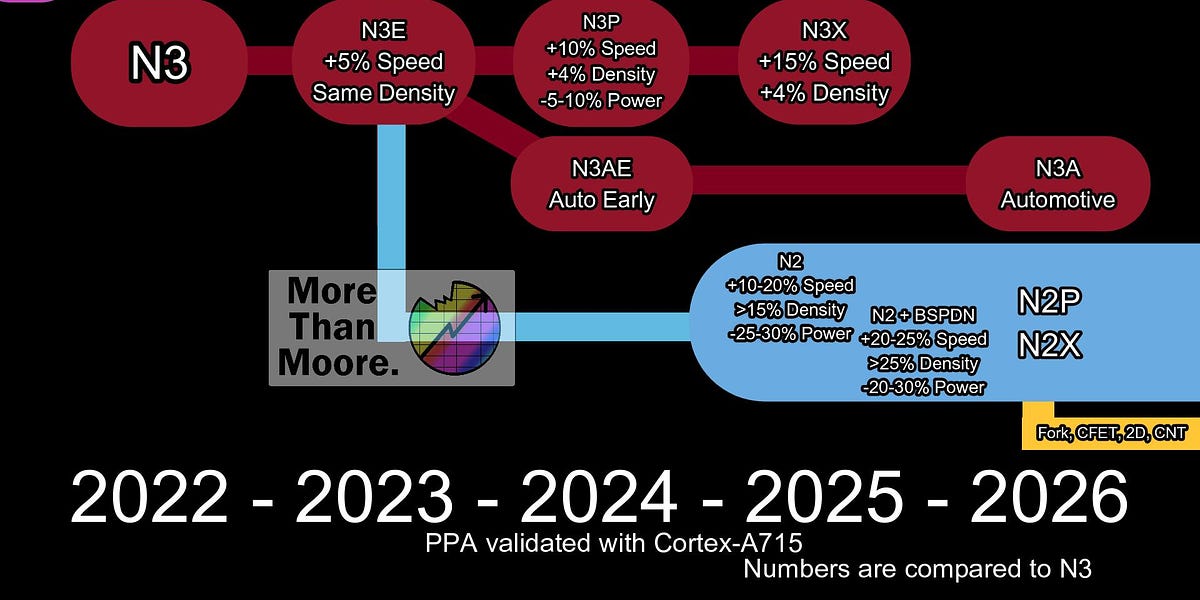

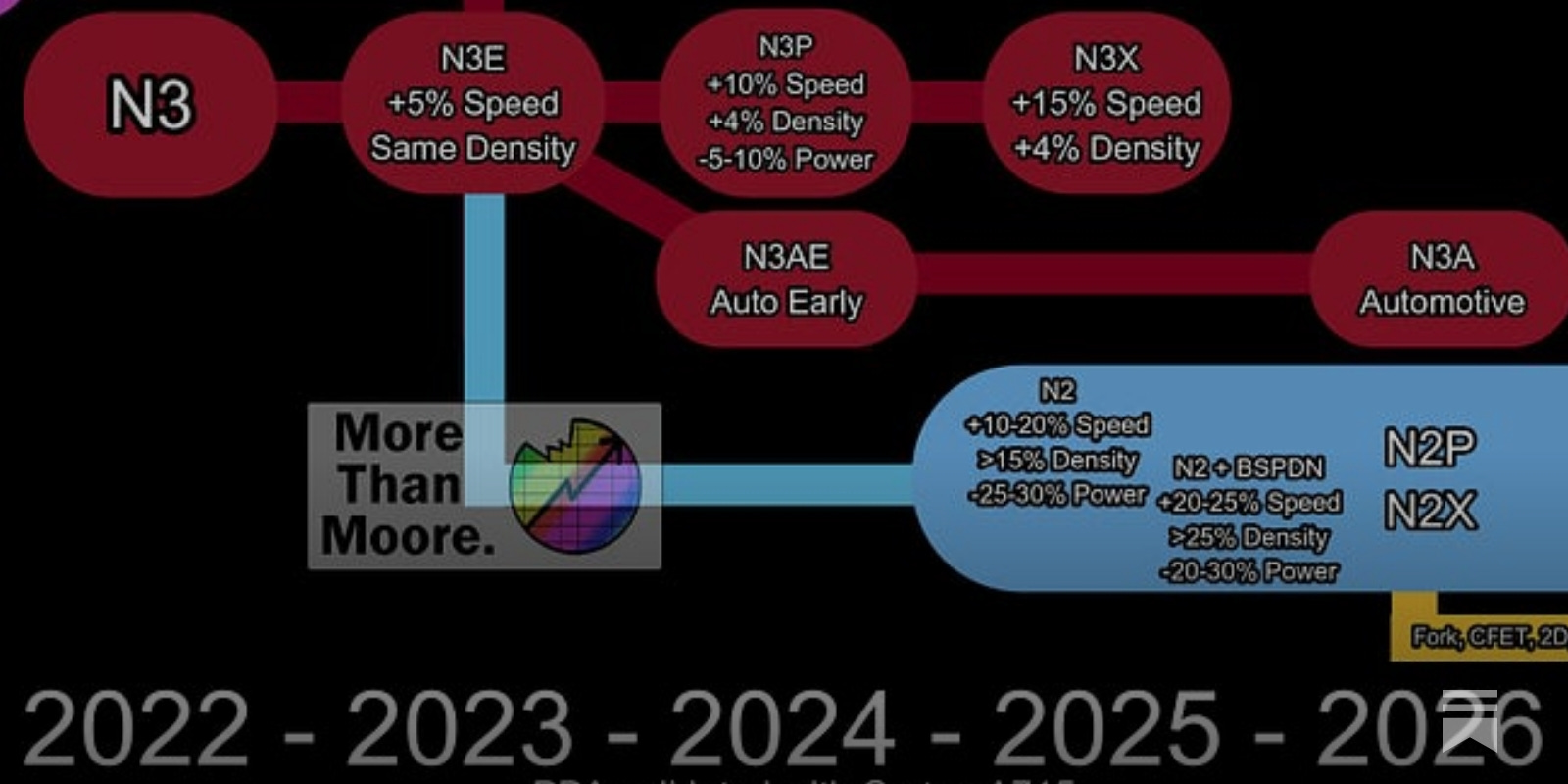

TSMC OIP Forum: Fabs, N3/N2+BSPN - by Dr. Ian Cutress

TSMC OIP Forum: Fabs, N3/N2+BSPN - by Dr. Ian Cutress

TSMC OIP Forum: Fabs, N3/N2+BSPN - by Dr. Ian Cutress

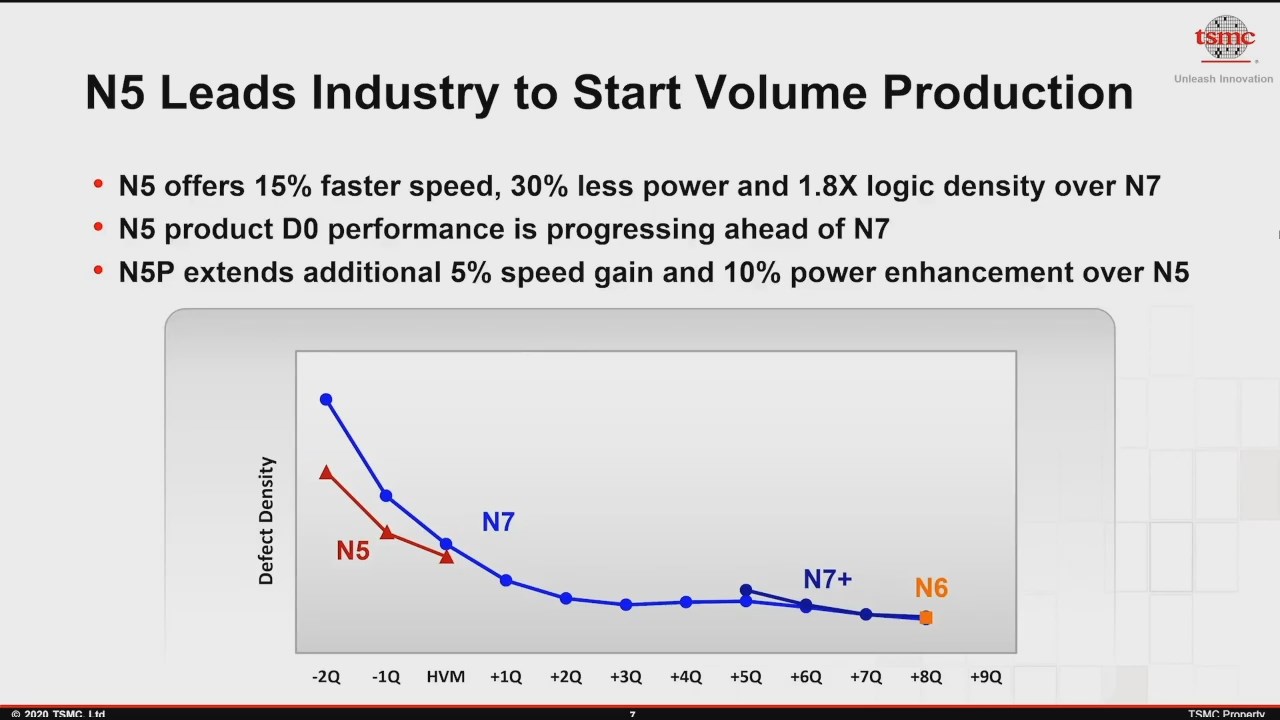

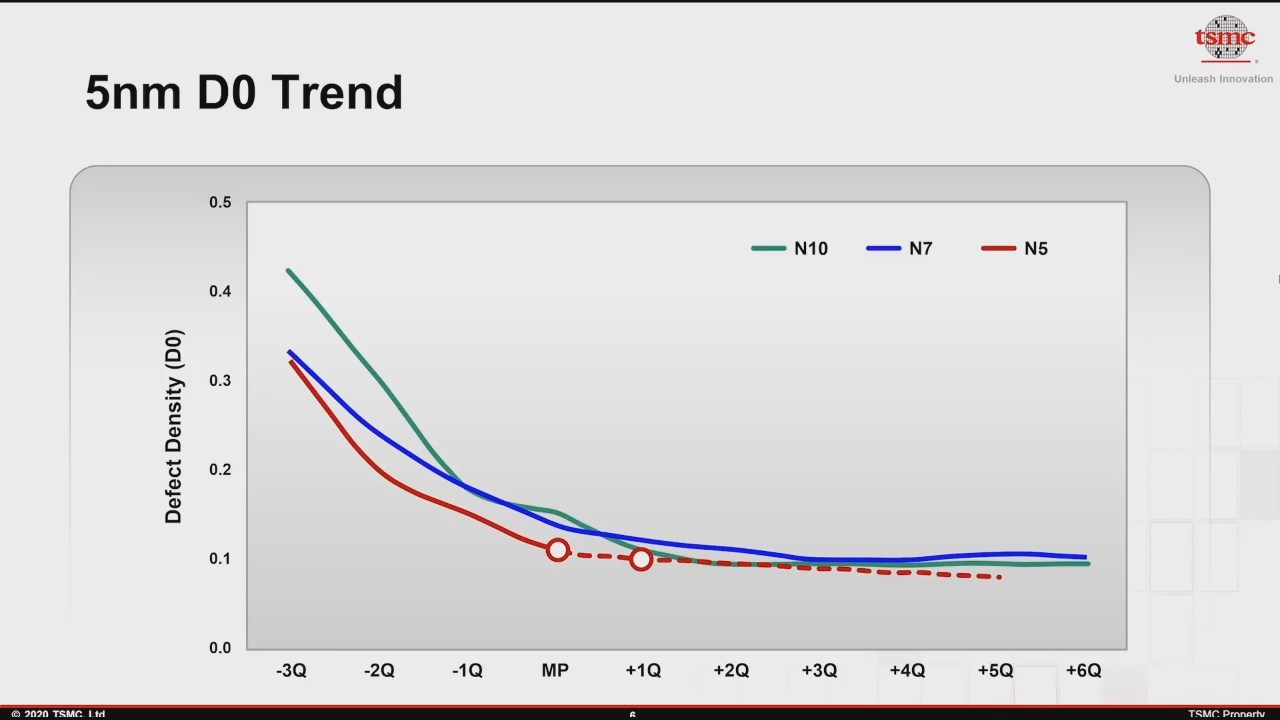

Better Yield on 5nm than 7nm': TSMC Update on Defect Rates for N5

TSMC OIP Forum: Fabs, N3/N2+BSPN - by Dr. Ian Cutress

TSMC OIP Forum: Fabs, N3/N2+BSPN - by Dr. Ian Cutress

TSMC OIP Forum: Fabs, N3/N2+BSPN - by Dr. Ian Cutress

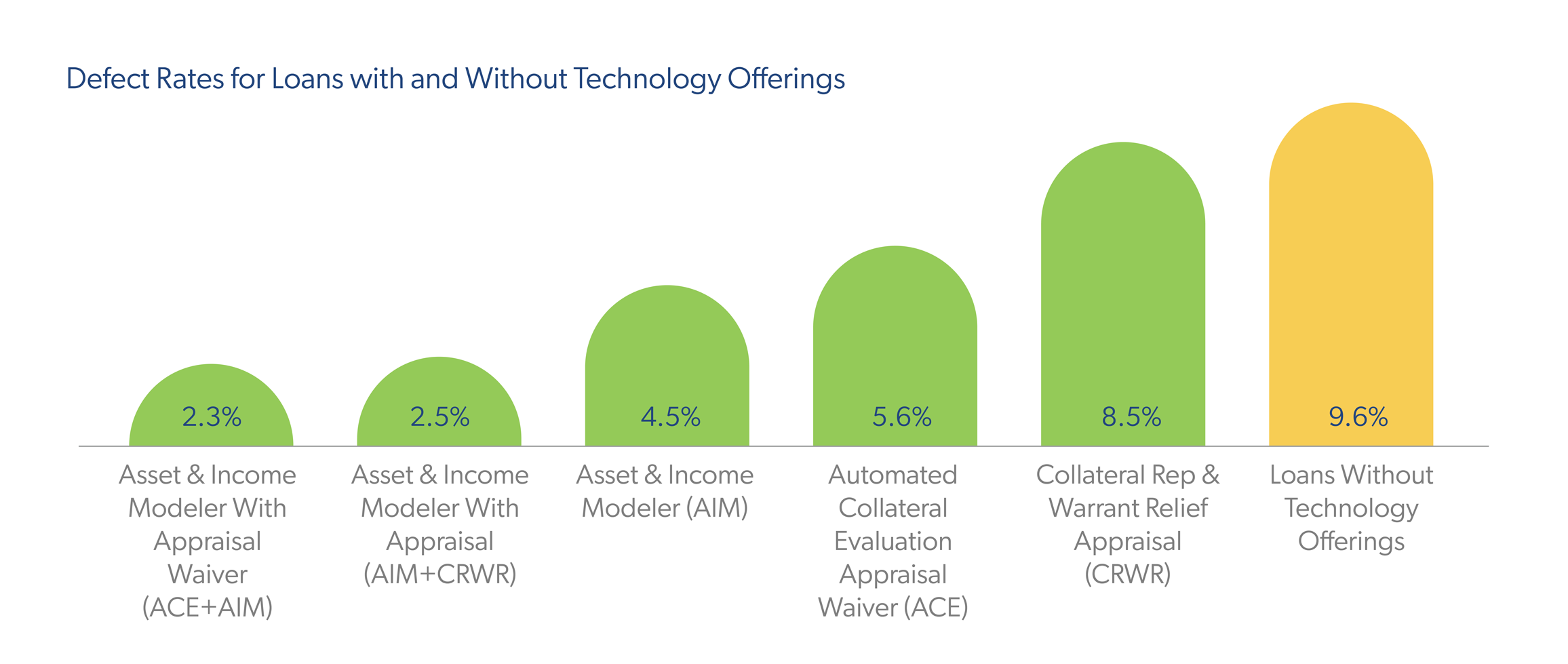

Better Yield on 5nm than 7nm': TSMC Update on Defect Rates for N5

𝐷𝑟. 𝐼𝑎𝑛 𝐶𝑢𝑡𝑟𝑒𝑠𝑠 on X: Here's a mockup of what was shown regarding TSMC's N4 D0 defect rate compared to previous nodes. Grey line shows high volume manufacturing start (N4 beyond HVM

Better Yield on 5nm than 7nm': TSMC Update on Defect Rates for N5

TSMC OIP Forum: Fabs, N3/N2+BSPN - by Dr. Ian Cutress

TSMC OIP Forum: Fabs, N3/N2+BSPN - by Dr. Ian Cutress